AMD presenta i suoi nuovi processori per server Epyc in occasione di un evento indoor a San Francisco. Epyc 98×4 basato su Zen 4c “Bergamo” ha fino a 128 core incluso il multi-threading simultaneo, quindi fornisce fino a 256 thread. Genoa-X come Epyc 9684X ha fino a 1.125 GB di cache L3.

I processori Epyc Bergamo e Genoa-X sono compatibili con la stessa piattaforma Genoa e possono essere eseguiti dopo l’aggiornamento del BIOS. Ciò consente ai clienti di combinare facilmente i propri server rack durante l’esecuzione di carichi di lavoro diversi.

Gli AMD Epyc esistenti vengono ora utilizzati anche per visualizzare in anteprima le istanze M7a di EC2 su Amazon AWS Cloud. Dovrebbe raggiungere prestazioni superiori del 50% rispetto a M6a con Epyc precedenti ed essere le istanze x86 più veloci nella gamma di Amazon. Oracle Cloud vuole seguire l’esempio con le istanze E5 a partire da luglio. Microsoft vuole anche che Genoa-X venga utilizzato immediatamente su istanze HBv4/HX nel suo cloud Azure e promette un salto di prestazioni rispetto a HBv3 con Milan-X fino a un fattore di 5,7 in NASTRAN, un’applicazione per la simulazione che utilizza metodo degli elementi finiti.

Gli attuali processori Genoa si stanno già comportando molto bene rispetto ai processori Intel Xeon. AMD si vede con un vantaggio del 90 percento in AMD SPECpower_ssj 2008, soprattutto in termini di efficienza energetica. Questi partner cloud apprezzano anche l’elevata efficienza energetica in quanto riduce i costi operativi.

Oltre al normale Epyc 9004 (vedi sotto per i dettagli sulla tecnologia), AMD ora vende anche filiali specializzate Bergamo e Genova-X. Per le telecomunicazioni e le applicazioni di fascia alta, Siena verrà aggiunta nella seconda metà del 2023 con miglioramenti più speciali. Tuttavia, AMD tace ancora su questo.

Epyc 97×4: Rapid Bergamo con 256 CPU

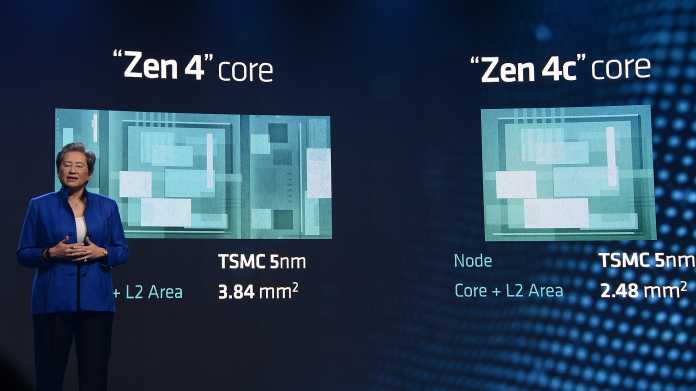

Il core 4c, inclusa la cache L2, è circa il 35% più piccolo dello Zen 4

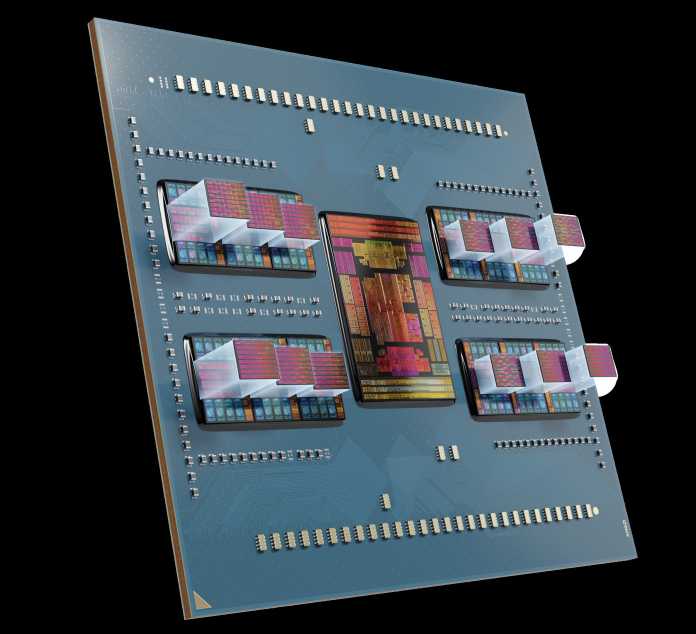

Bergamo è una Genova rivista e quindi ha uno Zen 4 core. Tuttavia, AMD ha migliorato il layout del circuito dei core Zen 4c e aumentato notevolmente la densità delle celle utilizzate. I progettisti di chip possono ora integrare 32 core invece dei precedenti 16 core in un cache compute die (CCD). Tuttavia, la cache L3 rimane a 32 MB. Ogni blocco da 16 MB appartiene a una partizione a 16 core (CCX), come nelle precedenti generazioni Zen, ci sono due partizioni CCX per CCD che comunicano tra loro tramite Infinity Fabric invece che direttamente. Ciò semplifica la progettazione della cache L3 e consente una maggiore densità di transistor, ma riduce la latenza quando i dati devono passare da un CCX a un altro. A Bergamo sono stati installati in totale 82 miliardi di transistor.

Bergamo utilizza core Zen 4c ottimizzati per le prestazioni per watt.

(Immagine: AMD)

In termini di prestazioni, AMD afferma di avere la CPU server più veloce con Bergamo e il suo 128 Zen 4c quando si tratta di valori benchmark CPU SPECrate 2017 nel sistema int_base, ovvero calcoli corretti con un set limitato di ottimizzazioni. Un singolo Epyc 9754 dovrebbe raggiungere 981,4 punti, un sistema 2P 1950. Con la stessa potenza di progettazione termica fino a 400 W, a seconda del carico di lavoro, i dispositivi Bergamo Epyc possono funzionare in modo più efficiente rispetto al noto Epyc 9004.

AMD vede Bergamo-Epyc 97×4 principalmente nei data center cloud, dove, ad esempio, molte macchine virtuali vengono eseguite in parallelo con set di core fissi. Con l’Epyc 97×4, l’azienda vuole tenere sotto controllo i processori per server ARM, ma anche l’Altra Max di Ampere, anch’esso dotato di 128 core, o un imminente 192 con tecnologia RISC-V della startup statunitense Ventana Micro. AMD può annunciare Bergamo solo con il maggior numero di processori logici o CPU virtuali per versione, perché a differenza dei server ARM o RISC-V, Bergamo gestisce il multithreading concorrente (SMT) e fornisce al sistema operativo un core virtuale per ogni core fisico. Ciò consente una migliore compensazione per la latenza della memoria e l’utilizzo delle unità aritmetiche. Tuttavia, alcuni fornitori di servizi cloud non utilizzano SMT per motivi di sicurezza, poiché SMT facilita alcuni attacchi del canale laterale.

Genoa-X con molta cache

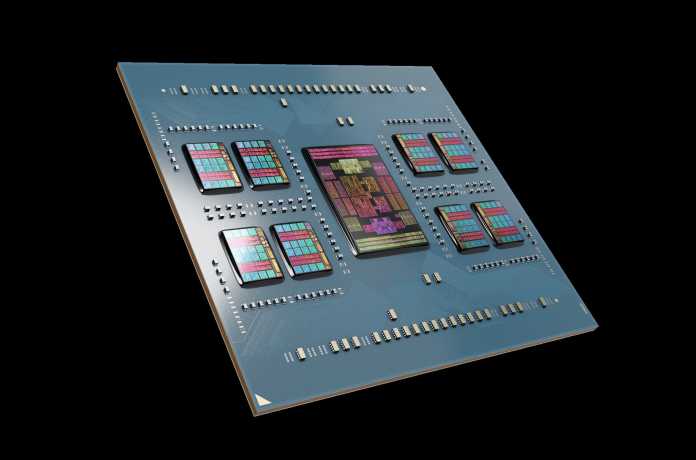

La tecnologia 3D o V-Cache di AMD ha effettivamente fatto il suo debutto nelle CPU server Milan-X ed Epyc 7xx3X della generazione precedente. Viene riutilizzato nel die di Genova ed espande la cache L3 per ciascuno dei dodici CCD da 32 a 96 MB. La CPU può quindi accedere a un massimo di 1152 MB di cache L3.

AMD Epyc 9004: cache L3 aumentata a 1.125 GB con moduli 3D V-Cache aggiuntivi.

(Immagine: AMD)

Non tutte le applicazioni beneficiano allo stesso modo di cache di grandi dimensioni; AMD vede Genoa-X principalmente nei calcoli tecnici, come la progettazione del prodotto, l’analisi strutturale, l’aerodinamica o altre simulazioni. Non sostituisce il normale Epyc 9004, ma viene offerto in aggiunta ad esso. A causa dell’ampia memoria cache, alcune applicazioni devono essere eseguite fino al doppio della velocità, il che raddoppia anche la produttività per ogni giorno lavorativo. Questo non solo rende possibile creare sistemi server più veloci, ma anche più efficienti dal punto di vista energetico.

Secondo AMD, l’Epyc 9964X di fascia alta dovrebbe superare l’Intel Xeon Platinum 8480+ e anche l’8490H a 60 core in tali applicazioni. La stessa AMD parla di un fattore di 2,2 (ovvero il 120 percento in più) con OpenFOAM fino a 2,9 volte in Ansys Fluent. La tecnologia V-cache di AMD utilizza silicio-thru-slot (TSV), ovvero connessioni verticali passanti, per collegare un altro chip di silicio con una cache ottimizzata per regione sopra la normale cache di livello 3 da 32 MB a Genova.

La tecnologia di impilamento di TSMC consente una densità di contatto estremamente elevata e non richiede connessioni saldate. Invece, i chip sono posizionati direttamente uno sopra l’altro con collegamenti diretti in rame. Secondo AMD, il chip cache aggiuntivo non richiede alcuna logica aggiuntiva come tag L3 o simili; Quindi può essere costruito in modo più compatto. Pertanto, occupa 64 MB invece dei 32 MB extra per chip.

Tecnologia Zen4

Epyc 9004 per la versione SP5 ha core CPU di generazione Zen 4, che sono migliorati rispetto a Zen 3. Grazie alla tecnologia di micro produzione TSMC N5 invece di N7, c’è il doppio della cache L2: 1 MB per core invece di 0,5 MB di byte precedenti. La cache L3 è rimasta a 32 MB per otto core, che si trovano insieme su un core complex die (CCD). Proprio come gli Xeon di Intel, i core Zen 4 ora elaborano sia le istruzioni AVX-512, le istruzioni Vector Neural Network (VNNI) sia la formattazione dei dati BFloat16 (BF16) per gli algoritmi AI.

Mentre gli Xeon più potenti (ma non tutti) hanno ciascuno due unità di calcolo AVX-512 per core della CPU, AMD raggruppa insieme due unità di calcolo AVX2 per l’AVX-512. Con la stessa frequenza di clock, il core Xeon può elaborare il doppio delle istruzioni AVX-512 rispetto al core Epyc. Tuttavia, poiché gli Xeon vengono sincronizzati in meno tempo durante l’elaborazione del codice AVX-512 rispetto ad altri codici, il vantaggio non è così grande.

Non solo Genoa-IOD ha collegamenti Infinity Fabric più numerosi e più veloci per i dispositivi CCD, ma fornisce anche velocità di trasferimento dati molto più elevate in memoria (RAM) e PCI Express (PCIe). Perché invece dei precedenti otto canali di memoria DDR4-3200, ora ci sono dodici canali per DDR5-4800 e quindi una velocità di trasferimento dati superiore del 125% di 460 invece di 204 GB / s.

64 dei 128 slot PCIe supportano anche Compute Express Link (CXL). Ciò consente agli acceleratori di calcolo di comunicare in modo coerente con la cache, il che aumenta l’efficienza: i dati non devono essere copiati avanti e indietro così spesso. Ciò che è ancora più importante con Epyc 9004 è che CXL può anche collegare moduli DRAM aggiuntivi e SSD ultraveloci con funzioni speciali, come la memoria della classe di archiviazione (SCM) e l’archiviazione computazionale.

(csp)

“Incurable thinker. Food enthusiast. Subtly charming alcohol scholar. Pop culture advocate.”

More Stories

Ecco come vivere l’eclissi di superluna il 18 settembre

Santa Monica dà il benvenuto ai giocatori PC con nuove funzionalità

Microcontrollori: collaborazione in tempo reale nel cloud Arduino